使用

程序人生

权限

两轮自平衡小车设计

wpf

binder

节日

.netcore

yarn

SylixOS

rockchip

学习方法

g2o优化

CSDN

函数替换

中断

react

BP神经计算

web网页设计期末课程大作业

OSPF

高速接口

2024/4/25 22:12:40Xilinx平台Aurora IP介绍(汇总篇)

Aurora IP核使用超简单的,COME ON! 目录

一、Xilinx平台Aurora IP介绍(一)Aurora基础知识

二、Xilinx平台Aurora IP介绍(二)时钟与复位

三、Xilinx平台Aurora IP介绍(三)Aurora配…

紫光同创FPGA实现HSSTLP高速接口通信,8b/10b编解码数据回环,提供PDS工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、设计思路框架HSSTLP详解HSSTLP基本了解HSSTLP之时钟HSSTLP之PCSHSSTLP之PMAHSSTLP之接口说明 硬件设计HSSTLP IP调用和配置 4、PDS工程详解5、上板调试验证并演示6、福利:工程代码的获取 紫光同创FPGA实…

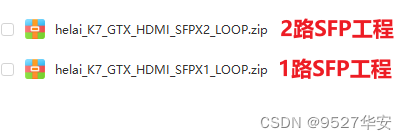

FPGA GTX全网最细讲解,aurora 8b/10b协议,HDMI视频传输,提供2套工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、GTX 全网最细解读GTX 基本结构GTX 发送和接收处理流程GTX 的参考时钟GTX 发送接口GTX 接收接口GTX IP核调用和使用 4、设计思路框架视频源选择IT6802解码芯片配置及采集动态彩条视频数据组包GTX aurora 8b/10b数据…

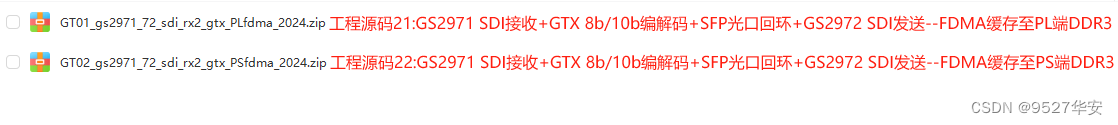

FPGA高端项目:FPGA基于GS2971+GS2972架构的SDI视频收发+GTX 8b/10b编解码SFP光口传输,提供2套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐本博主所有FPGA工程项目-->汇总目录本博已有的 SDI 编解码方案本方案的SDI接收发送本方案的SDI接收图像缩放应用本方案的SDI接收纯verilog图像缩放纯verilog多路视频拼接应用本方案的SDI接收HLS图像缩放HLS多路视频拼接应用本方案的SDI…

ZYNQ--GT收发器(TX)

文章目录 Tx通道关于数据宽度设置关于TXUSRCLK and TXUSRCLK2 Generation8B/10B编码K字符TX Gearbox(后面再讨论64B/66B)TX BufferTX Buffer Bypass(暂时不讨论)TX Polarity ControlTX Fabric Clock Output ControlTX Configurable DriverTx通道

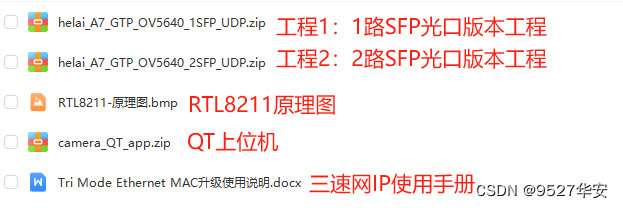

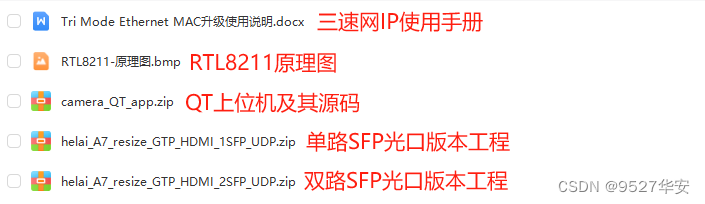

FPGA高端项目:图像采集+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

目录 1、前言免责声明本项目特点 2、相关方案推荐我这里已有的 GT 高速接口解决方案我这里已有的以太网方案 3、设计思路框架设计框图视频源选择OV5640摄像头配置及采集动态彩条视频数据组包GTP 全网最细解读GTP 基本结构GTP 发送和接收处理流程GTP 的参考时钟GTP 发送接口GTP …

FPGA高端项目:图像缩放+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

目录 1、前言免责声明本项目特点 2、相关方案推荐我这里已有的 GT 高速接口解决方案我这里已有的以太网方案我这里已有的图像处理方案 3、设计思路框架设计框图视频源选择ADV7611 解码芯片配置及采集动态彩条跨时钟FIFO图像缩放模块详解设计框图代码框图2种插值算法的整合与选择…

Xilinx平台Aurora IP介绍(二)时钟与复位

时钟,又见时钟。 汇总篇:

Xilinx平台Aurora IP介绍(汇总篇) 目录

前言

一、Aurora核的时钟

二、复位设计

后记 前言 为什么每次都将时钟和复位单独拿出来讲? 对于我们使用Xilinx或其他的成熟IP而言,IP…

Xilinx平台Aurora IP介绍(一)Aurora基础知识

Aurora IP使用起来超简单的,Come On! 汇总篇:

Xilinx平台Aurora IP介绍(汇总篇) 目录

一、Aurora协议

二、Xilinx平台Aurora IP介绍

三、Aurora IP组成结构

3.1总览

3.2框图

3.3顶层结构 一、Aurora协议 Auro…

Xilinx平台Aurora IP介绍(四)Example Design介绍

多看一些example design之后,你就会发现都是熟悉的配方~ 汇总篇:

Xilinx平台Aurora IP介绍(汇总篇) 目录

一、Example Design

二、仿真 一、Example Design

首先打开example design,看看示例工程架构: …

Xilinx平台Aurora IP介绍(三)Aurora配置及接口介绍

来咯来咯,搬砖全靠它! 汇总篇:

Xilinx平台Aurora IP介绍(汇总篇) 目录

一、Aurora配置

1.1第一页配置

1.2第二页配置

1.3第三页配置

二、Framing接口

2.1 接口信号

2.2理论介绍

2.3 接口时序图

三、Streamin…

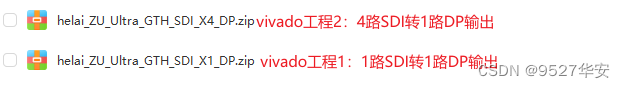

FPGA高端项目:UltraScale GTH + SDI 视频解码,SDI转DP输出,提供2套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐我这里已有的 GT 高速接口解决方案我目前已有的SDI编解码方案 3、详细设计方案设计框图3G-SDI摄像头LMH0384均衡EQUltraScale GTH 的SDI模式应用UltraScale GTH 基本结构参考时钟的选择和分配UltraScale GTH 发送和接收处理流程UltraScale…

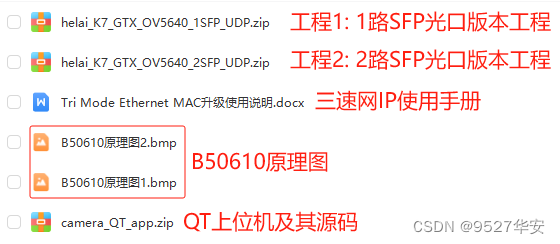

FPGA高端项目:图像采集+GTX+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

目录 1、前言免责声明本项目特点 2、相关方案推荐我这里已有的 GT 高速接口解决方案我这里已有的以太网方案 3、设计思路框架设计框图视频源选择OV5640摄像头配置及采集动态彩条视频数据组包GTX 全网最细解读GTX 基本结构GTX 发送和接收处理流程GTX 的参考时钟GTX 发送接口GTX …

紫光同创FPGA实现HSSTLP高速接口视频传输,8b/10b编解码,OV5640采集,提供PDS工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、设计思路框架设计框图OV5640摄像头配置及采集视频数据封装按键选择HSSTLP高速收发器详解HSSTLP基本了解HSSTLP之时钟HSSTLP之PCSHSSTLP之PMAHSSTLP之接口说明硬件设计HSSTLP IP调用和配置 SFP连接方案选择视频数据…